M-3

# 実装を考慮した細胞体モデルに対する一検討 A Study on a Cell Body Model Considering IC Implementation

○戸泉孝太 ¹,佐伯勝敏 ²,関根好文 ³ \*Takahiro Toizumi¹,Katsutoshi Saeki²,Yoshifumi Sekine³

Abstract: Since neural networks have superior information processing function, many investigators attempt to model biological neurons and their networks. Furthermore, a number of studies of neural networks have recently been undertaken with the purpose of applying engineering to the brain. When the large scale Artificial Neural Network (ANN) is constructed, it is desirable that mounting area of cell body model constructing the ANN is small.

In this paper, we reduce the gate voltage of NMOS as a negative resistance device for the purpose of constructing a cell body model with IC. As a result, we kept gate voltage of NMOS as a negative resistance device to less than 2[V]. Moreover, mounting area of a cell body model is reduced to about 2%, when compared with previous model.

## 1. まえがき

近年,生体の情報処理機構をモデル化し,工学的に応用しようとする研究が行われている<sup>[1]</sup>.しかし,生体の情報処理機構をモデル化する場合,大規模なニューラルネットワークを構築する必要がある.そのため,細胞体モデル一つの実装面積は小さいことが望ましい.

しかし、先に我々が提案した実装面積を削減した細胞体モデル<sup>[2]</sup>は、チップ化を行った場合、負性抵抗素子のNチャネル型 MOSFET(以下 NMOS)のゲートに耐圧以上の電圧がかかっているため、発振しなかった.

今回、実装を考慮し、負性抵抗素子のNMOSのゲートの電圧を低下させた細胞体モデルの構築について検討を行った。

### 2. 本論

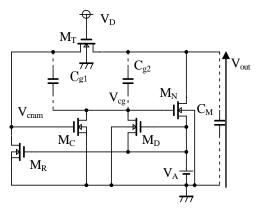

Figure.1 に今回提案する負性抵抗素子の NMOS のゲートの電圧を低下させた細胞体モデルを示す. 同図において,  $M_N$ の W/L=50,  $M_C$ の W/L=0.5,  $M_C$ の W/L=0.8,  $M_R$ の W/L=0.67,  $M_T$ の W/L=7.5 とし, 電源  $V_A=V_D=1.8[V]$ としている. また同図において  $C_M$ ,  $C_{g1}$ ,  $C_{g2}$ は寄生容量で構成されている.

Figure.1 Cell body model

Figure.1 の細胞体モデルの動作原理を以下に示す. ま ず初期状態として  $V_{\text{out}}=V_{\text{ce}}=V_{\text{cram}}=0[V]$ とすると, $M_T$ と M<sub>R</sub>のドレインーソース間には電位差が生じていない ため、 $M_T$ と  $M_R$ のドレインーソース間には電流が流れ ない. また  $M_N$  のゲート-ソース間の電位差も 0[V]で あるため、 $M_N$ のドレイン-ソース間にも電流がほとん ど流れない. その状態から  $V_A$ により  $M_D$ を通って,  $C_{gl}$ ,  $C_{g2}$ に電荷が蓄積される.  $C_{g2}$ を通った電荷は,  $M_T$ ,  $M_R$ のドレインーソース間を流れられないため、 $C_M$ に流れ 込む.  $C_M$  に電荷が溜まることで、 $V_{out}$  が少し立ち上が り、M<sub>T</sub>、M<sub>R</sub>のドレイン-ソース間に電位差が生じる ため、 $M_T$ 、 $M_R$  に電流が流れ始める.  $V_A$  により  $C_{gl}$ 、  $C_{g2}$  に電荷が蓄積されることで、 $M_N$  のゲートーソース 間に $M_N$ の閾値以上の電圧がかかり、 $M_N$ のドレインー ソース間に大きな電流が流れ始める.このとき、 $M_N$ のアスペクト比は  $M_T$ ,  $M_R$  のアスペクト比よりも大き いため、 $M_T$ 、 $M_R$ を流れられない余剰分の電流が $C_M$ に 流れ込み、 $V_{out}$ が立ち上がる。 $V_{out}$ が立ち上がると $V_{cram}$ も立ち上がり、Mcのゲートーソース間にも閾値以上の 電圧がかかり、 $M_C$ が起動する.  $M_C$ が起動することで、  $C_{gl}$ ,  $C_{g2}$ から電荷を引く抜く.  $C_{g2}$ から電荷が引き抜か れたことにより、 $M_N$ のゲート-ソース間の電位差が 0[V]に近づき、 $M_N$ のドレイン-ソース間には、ほとん ど電流が流れなくなる.  $V_{out}$ に溜まった電荷は $M_T$ ,  $M_R$ から引き抜かれることで、 $V_{out}$  が立下り、 $V_{cram}$  も立ち 下がる. すると  $M_C$  は OFF となり, 再び  $V_A$  により  $C_{gl}$ , Cg2 に電荷が蓄積されることで発振を繰り返す.

Figure.1 において、 $M_T$ がない状態でも、アスペクト比を調整することで、シミュレーション上では発振を行うことができる。しかし $M_T$ がない場合、 $M_N$ のゲート電位  $V_{cg}$  に約 5[V]程度の電圧がかかってしまう。今

回使用しているNMOSのゲートの耐圧は約2[V]程度で あるため, チップ化を行った場合, 耐圧以上の電圧が かかり、発振を行わないと考えられる. しかし、 $M_T$ を 挿入することで  $V_{cg}$  を低下させることができる. 寄生 容量の発生する場所として MOS の端子間が挙げられ る. このことから、 $C_{g1}$ 、 $C_{g2}$ はそれぞれ $M_{C}$ のゲートー ドレイン間の寄生容量と M<sub>N</sub> のゲート-ソース間の寄 生容量で構成されていると考えられる. M<sub>T</sub>がない場合,  $C_{g1}$  と  $C_{g2}$  は統合され、 $V_{out}$  と  $V_{cg}$  間に寄生容量が発生す る. このとき  $M_N$  のゲート電位  $V_{cg}$  は  $C_M$  にかかる電圧 と  $V_{out}$  と  $V_{cg}$  間に発生した寄生容量にかかる電圧の和 と表すことができる.  $M_T$ を挿入した場合,  $V_{cram}$ は  $V_{out}$ より低い電位にクランプされる. また  $M_C$  のゲートを  $V_{cram}$ に接続することで $V_{out}$ - $V_{cg}$ 間に発生していた寄生 容量を  $C_{g1}$  と  $C_{g2}$  に分割することができる. 分割され  $V_{cram} - V_{cg}$ 間にコンデンサが接続されたことにより, $V_{cg}$ が  $V_{out}$  より電位の低い点である  $V_{cram}$  の影響を受けるこ とで $V_{cg}$ が低下する. また $M_N$ のアスペクト比を大きく することで、 $M_C$ の起動が速くなり  $V_{cg}$  が低下する.

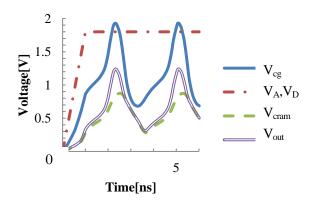

Figure.2 に今回提案する細胞体モデルの特性を示す. 同図から、 $V_{out}$ が発振を繰り返していることがわかる. また、負性抵抗素子としての役割を持つ  $M_N$  のゲート電位である  $V_{cg}$  が NMOS の耐圧である 2[V]以下に抑えられていることがわかる. このことから、今回提案する細胞体モデルは NMOS のゲートの耐圧を考慮できているといえる.

Figure.2 Cell body model characteristics

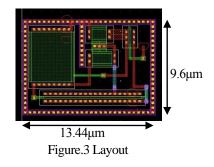

Figure.3 に今回提案する細胞体モデルのレイアウト 図を示す. 同図において, 縦は  $9.6 [\mu m]$ , 横は  $13.44 [\mu m]$  となっており, 実装面積は  $129 [\mu m^2]$  となる. 先に提案 したモデルの実装面積は  $132 [\mu m^2]$  となるため, 実装面積を 2%程度削減できている.

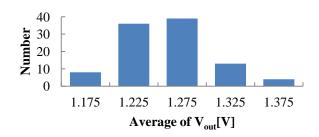

Figure 4 に今回提案する細胞体モデルのモンテカルロ解析の結果を示す。同図において、横軸は  $V_{out}$  のピーク値の範囲の平均値を示し、例えば 1.275[V]の場合、1.25~1.3[V]の範囲で  $V_{out}$  のピーク値が発振を行っている細胞体モデルを示す。縦軸は発振を行っている細胞体モデルを示す。同図から、モンテカルロ解析を 100 回行った場合、100 回とも細胞体モデルが発振を行っているため、シミュレーション上では歩留まり率は 100% となった。

Figure.4 Monte Carlo analysis

### 3. まとめ

今回,実装を考慮した細胞体モデルの構築について 検討を行った.その結果,負性抵抗素子のNMOSのゲートにかかる電圧を低下させることで,NMOSの耐圧 である2[V]以下に抑え,また,実装面積は,先に提案 したモデルに比べ,2%程度削減できることを明らかにした.

今後は、今回検討を行った細胞体モデルを用いて、 大規模なニューラルネットワークを構築し、ニューロ ダイナミクスについて検討を行う予定である.

### 5. 参考文献

[1]伊藤真,黒岩丈介,三宅章吾: 「海馬を用いた記憶システムの神経回路網モデル」電子情報通信学会論文誌 Vol.J82-D-II(2), No.3、pp.276-286, 1999.

[2]奥山敦司,佐伯勝敏,関根好文:「大規模ANNのための細胞体モデルの面積削減に対する一検討」日本大学理工学部,学術講演会論文集,M-17,pp.1105-1106,2014.