C-12

# ソース不純物濃度がトンネル FET の ID-VD 特性に及ぼす影響

Influence of source impurity concentration on I<sub>D</sub>-V<sub>D</sub> characteristics in Tunnel FET

○三田 梓郎 <sup>1</sup>, 唐鎌亮太 <sup>1</sup>, 岸佳佑 <sup>1</sup>, 山口直弥 <sup>1</sup>, 呉研 <sup>2</sup>, 高橋芳浩 <sup>2</sup>

\* Shiro Mita <sup>1</sup>, Ryota Karakama <sup>1</sup>, Keisuke Kishi <sup>1</sup>, Naoya Yamaguchi <sup>1</sup>

Yan Wu <sup>2</sup>, Yoshihiro Takahashi <sup>2</sup>

Abstract: The switching characteristics of CMOS circuits using tunnel FETs are known to cause delays compared to MOSFETs, It is due to a gradual increase in  $I_D$ - $V_D$  characteristics. In this study, we examined whether the  $I_D$ - $V_D$  characteristics can be improved by changing the source impurity concentration.

#### 1. 序論

PCやスマートフォンの急速な発展はLSIの高集積化によって進められてきた. 高集積化が進んだLSIにおいては電源電圧の増加による消費電力の増大が問題となってくる. また近年普及が進んでいるIoTデバイスにおいても設置性や環境発電による微弱電力での動作が求められている. しかし現在ロジックCMOS LSIに用いられている MOSFETではこれ以上電源電圧を下げることは困難であることが分かっている. 理由として S. S. (sub-threshold slope)値が室温において,60 mV/dec. という原理的な限界をもつためである. これはソース端の電子がボルツマン分布することによって決まるためであり、オフ状態の電流値を上げずに電源電圧を下げるためにはS. S値が低い、すなわちオフ状態から急峻な立ち上がりを持ってオン状態へと移行できるsteep slope transistorの実現が求められている.

数多く研究が進められているsteep slope transistorの中でもMOSFETに作製工程が近く,宇宙空間や原子炉周辺などの強い放射線環境下で使用した場合でも寄生バイポーラ効果の影響を受けないといった特徴を持つトンネルFETは, 従来のMOSFETに比べ $I_D$ - $V_D$ 特性の立ち上がりが鈍ることが知られている.このようなデバイスを用いてCMOS回路を構成した場合,スイッチング速度は低くなることから,立ち上がり特性の改善は非常に重量である.そこで本研究では,Sourceの不純物濃度 $N_S$ が $I_D$ - $V_D$ 特性に及ぼす影響について検討を行った.

#### 2. デバイスシミュレーション

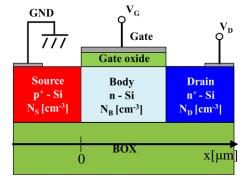

使用したデバイス構造の各パラメータをTable.1に示す. Source不純物濃度 $N_S$ による立ち上がり特性の検討を行うため $N_S$ を $1 \times 10^{19}$  [cm<sup>-3</sup>]から $1 \times 10^{21}$  [cm<sup>-3</sup>]と変化させ計算を行った. なお先行研究より,トンネルFETにおいてDrain電流を向上させるためには,急峻な接合界面が必要であることが確認されているため[\*],シミュレーション上において不純物濃度分布は階段接合として計算を行った.

Fig.1 Simulation model for Tunnel FET

Table.1 Simulation Parameter for Tunnel FET

| ゲート長LG               | 0. 25μm                            |

|----------------------|------------------------------------|

| ゲート幅W                | 1µm                                |

| Body不純物濃度NB          | $1 \times 10^{17} \text{cm}^{-3}$  |

| Drain不純物濃度ND         | $1 \times 10^{20}  \text{cm}^{-3}$ |

| SOI層T <sub>SOI</sub> | 0. 1µm                             |

| BOX層T <sub>BOX</sub> | 0. 3µm                             |

<sup>1:</sup> 日大理工・院(前)・電子, 2: 日大理工・教員・電子

## 3. 結果・考察

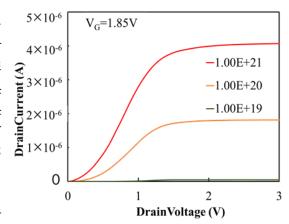

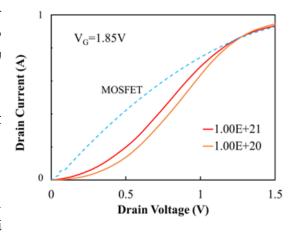

Fig.2にSource部の不純物濃度を変化させたときの $I_D$ - $V_D$ 特性を示す.結果より,Source不純物の高密度化に伴いON電流が増大することを確認した.また,不純物濃度変化が $I_D$ - $V_D$ 特性に及ぼす影響を評価するために, $V_D$ =3Vでのドレイン電流で正規化した結果をFig.3に示す.なお,従来のMOSFETの特性も併せて示す.結果より,Source不純物の高密度化に伴い,立ち上がり特性も改善可能であることがわかった.ただし,MOSFETに比べると立ち上がりに鈍く,CMOS回路適用時のスイッチング速度を考慮すると,更なる検討が必要である.

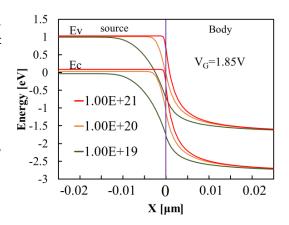

これまでに示した、Source部の不純物濃度が $I_D$ - $V_D$ 特性に及ぼす影響について考察するため、エネルギーバンド構造の変化について検討した。Fig.4にSource-Body接合界面付近のエネルギーバンド構造を示す.なお、本接合部分以外では、Source不純物による大きな変化は確認できなかった.Source不純物濃度を高密度化させていくと、Source-Body接合面(X=0)付近のエネルギーバンドの傾きが急峻になっていくことが確認できる.これはSource不純物濃度の高密度化により、Source領域での $p_D$ +接合の空乏層幅が狭くなるためである.これにより、バンド間トンネル距離が短くなり、トンネル確率が向上したため、 $I_D$ - $V_D$ +特性におけるON電流が増大し、かつ立ち上がり特性が改善したものと考えられる.

#### 4. まとめ

トンネルFETのSource不純物濃度が、 $I_D$ - $V_D$ 特性に及ぼす影響についてデバイスシミュレーションにより検討した。今回の検討範囲では、Source不純物濃度を $1\times10^{21}$ cm<sup>-3</sup>としたデバイスおいて、最も大きなON電流、及び急峻な $I_D$ - $V_D$ 立ち上がり特性を示すことを確認した。今後は、本手法がCMOS回路のスイッチング特性に及ぼす影響について検討を行うと共に、他の構造パラメータ依存性についても検討を行い更なる特性向上を目指す。

### 謝辞

本研究の一部は東京大学大規模集積システム設計教育研究センターを通し、シノプシス株式会社の協力で行われたものである.

# 参考文献

[1] 岩波悠太:「トンネルFETのデバイスパラメータが電気的特性 に及ぼす影響」, 平成29年度 日本大学理工学部学術講演会 論文

Fig.2 Source concentration dependence on  $I_D$ - $V_D$  characteristic

Fig.3 Normalized I<sub>D</sub>-V<sub>D</sub> Characteristics

Fig.4 Band structure on I<sub>D</sub>-V<sub>D</sub> characteristic